Syfala

Synthétiseurs Faible Latence sur FPGA

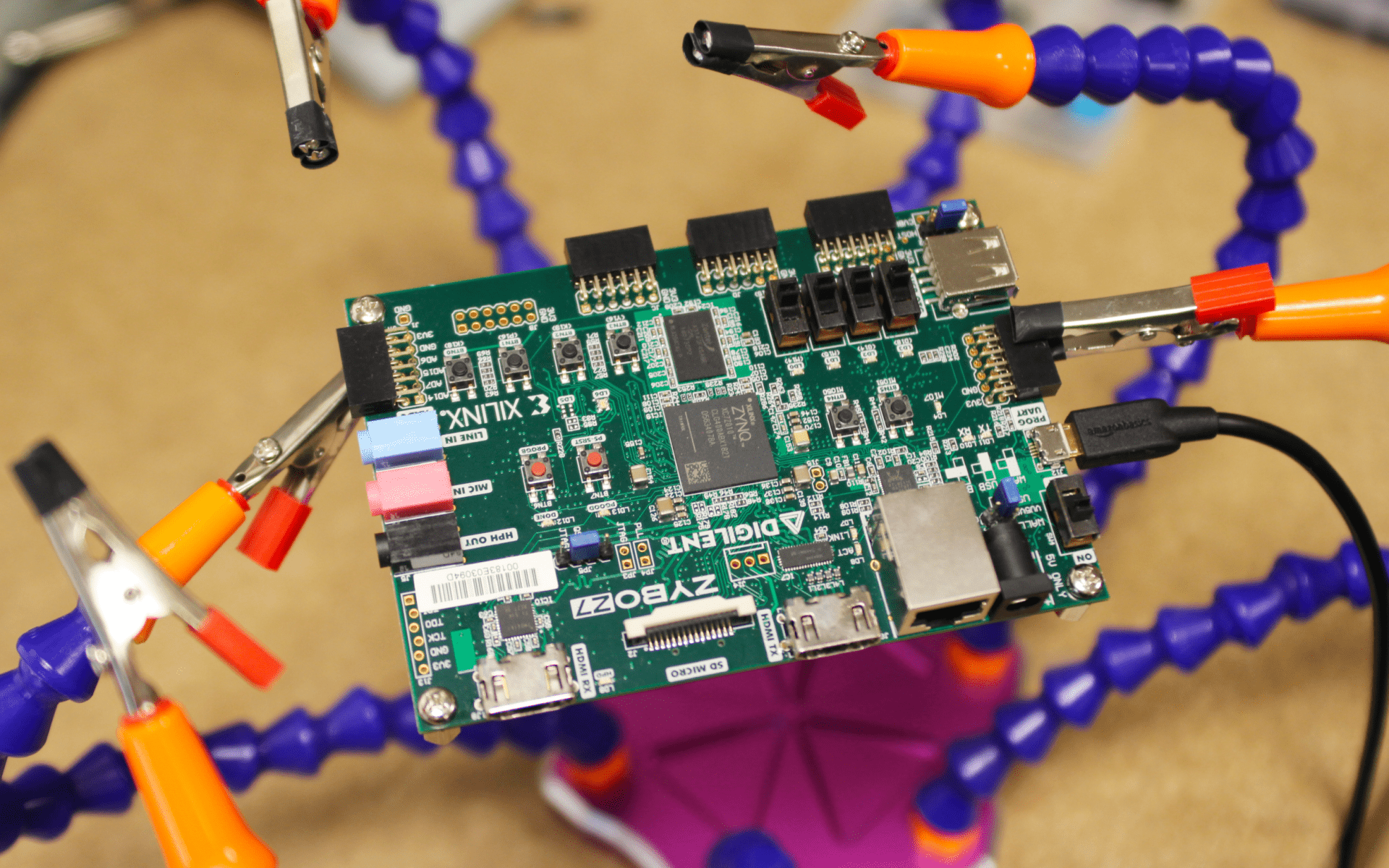

L’objectif du projet SyFaLa est de montrer que grâce à l’association des outils Faust (Grame) et Flopoco (Citi), il est possible de produire rapidement des systèmes pour le traitement numérique du signal en temps réel basse latence (quelques échantillons, moins de 50 microsecondes) en utilisant des cartes FPGA ayant une sortie audio. Un outil correctement assemblé pourrait ouvrir de nombreuses voies pour des effets programmables ou même pour une nouvelle manière de concevoir des synthétiseurs audio-numériques. Le porteur principal du projet est Tanguy Risset, professeur à l'INSA Lyon et membre du Laboratoire Citi. Florent De Dinechin (Citi), Kevin Marquet (Citi), Yann Orlarey (Grame), Stéphane Letz (Grame), Romain Michon (Grame) et Alain Darte (Xilinx) sont impliqués dans ce projet.

Partenaires : Grame CNCM, Lyon & Laboratoire Citi/INSA, Lyon

Date de début : 18/12/2018

Durée : 2 ans